- ❖ Describe when the dome/interior light of the car should be on.

- DriverDoorOpen = true if lefthand door open

- PassDoorOpen = true if righthand door open

- LightSwitch = true if light should be on regardless of door state, false if light should be on when a door is open

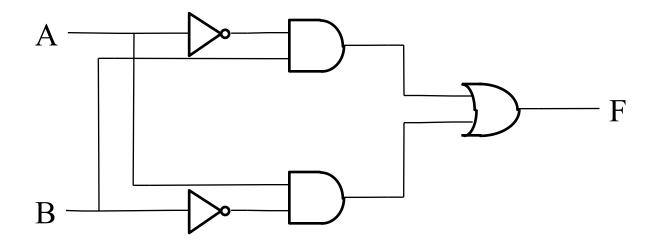

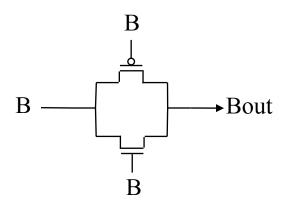

\* What does the following circuit do?

- \* To buy beer, someone must be of age. Which of these sentences tells us exactly when Ann and Bob can get beer?

- 1. It is not true that both Ann and Bob don't have ID.

- 2. Ann has ID or Bob has ID or Both have ID.

- 3. Ann has ID or Bob has ID

- 4. Ann has ID and Bob does not, or Bob has ID and Ann does not.

- 5. Ann has ID, or Bob has ID and Ann does not.

\* Create the truth table for an equality circuit, which is true whenever the two inputs are the same.

- ❖ Write the Boolean equation for the 2<sup>nd</sup> seat belt light circuit on slide 7

- Seat Belt Light (driver belt in, passenger belt in, passenger present):

\* Does the following Boolean equation implement the function given in the truth table?

$$MyCout' = (A*B) + (A*Cin) + (A*Cin)$$

| Α | В | Cin | Cout | MyCaw |

|---|---|-----|------|-------|

| 0 | 0 | 0   | 0    | 0     |

| 0 | 0 | 1   | 0    | 0     |

| 0 | 1 | 0   | 0    | 0     |

| 0 | 1 | 1   | 1    | 0     |

| 1 | 0 | 1   | 1    | 1     |

| 1 | 1 | 0   | 1    | t     |

| 1 | 1 | 1   | 1    | 110   |

|   |   |     |      |       |

Simplify the following Boolean Equation

$$AB + AC + AB$$

$$= AR + \overline{AR} + \overline{AC}$$

$$= \frac{A(R+q)}{A+\overline{A}}$$

$$= (A+\overline{A})R + AC$$

$$= R + AC$$

UNITY

Simplify the following Boolean Equation, starting with DeMorgan's Law

$$\overline{F} = A\overline{B} + AC$$

$$F = (A\overline{B}) + (AC) = (A\overline{B})(AC)$$

$$= (\overline{A} + B)(\overline{A} + \overline{C})$$

$$= \overline{A} + \overline{A}B + \overline{A}C + BC$$

$$= \overline{A} + BC$$

$$= \overline{A} + BC$$

$$ABS OZPTION$$

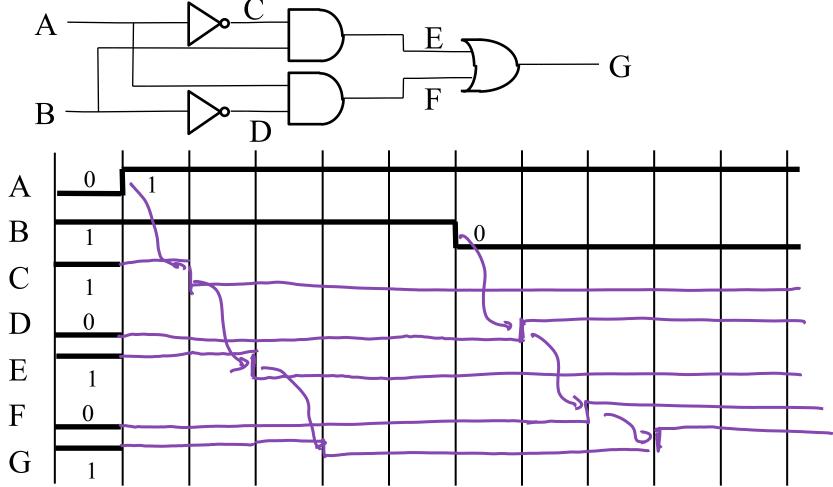

\* Assuming all gates have the same delay (including inverters), complete the following timing diagram.

\* Write the Verilog for a 2-input gate that is TRUE when an odd number of inputs are true.

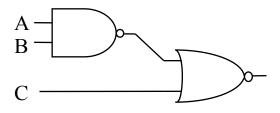

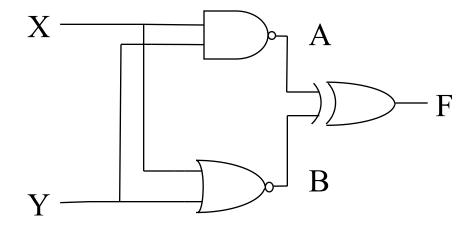

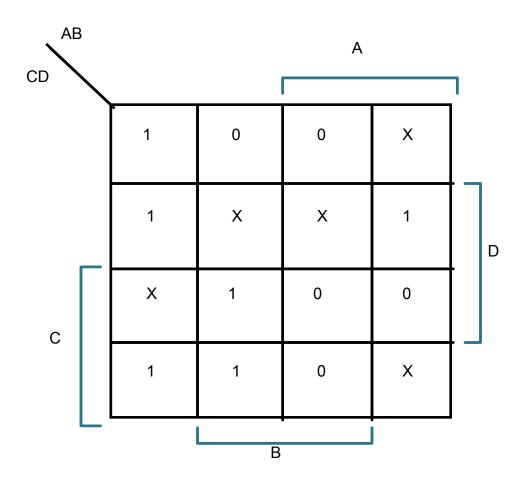

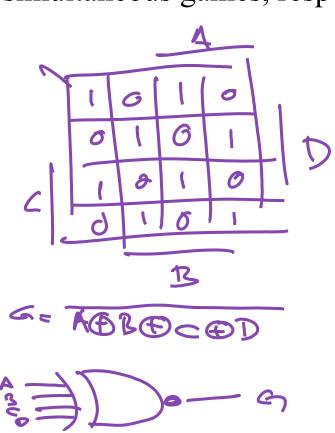

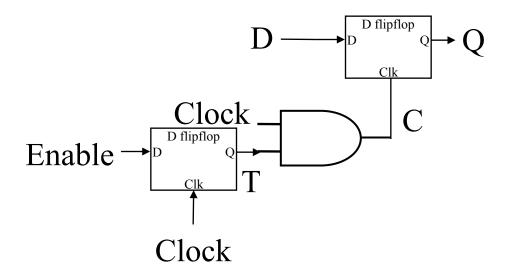

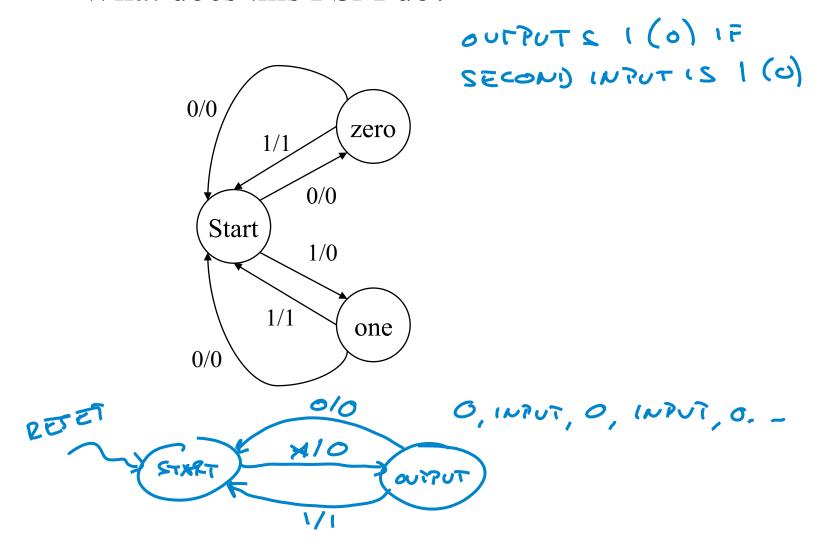

\* What does this circuit do?

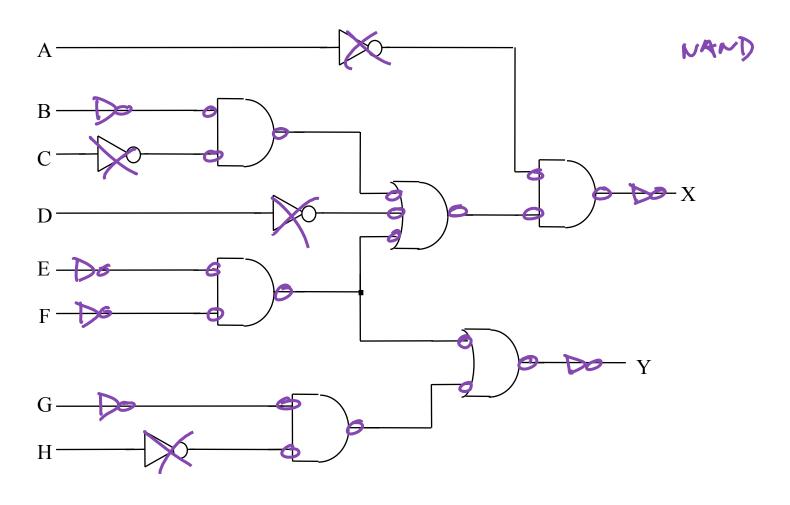

Convert the following circuit to NAND/NOR form

\* What does this circuit do?

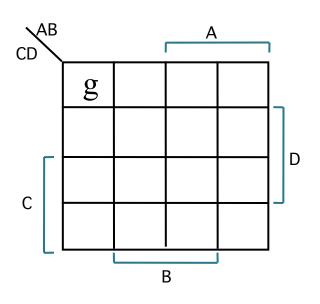

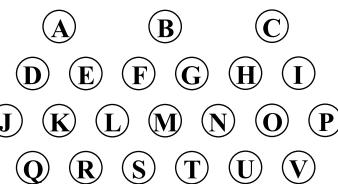

- ❖ Convert the Truth Table to a K-Map.

- \* Letters are used as variables to hold the function value

- First value already filled in.

| <u>A</u> | В | C | D | F |

|----------|---|---|---|---|

| 0        | 0 | 0 | 0 | g |

| 0        | 0 | 0 | 1 | h |

| 0        | 0 | 1 | 0 | i |

| 0        | 0 | 1 | 1 | j |

| 0        | 1 | 0 | 0 | k |

| 0        | 1 | 0 | 1 | 1 |

| 0        | 1 | 1 | 0 | m |

| 0        | 1 | 1 | 1 | n |

| 1        | 0 | 0 | 0 | 0 |

| 1        | 0 | 0 | 1 | p |

| 1        | 0 | 1 | 0 | q |

| 1        | 0 | 1 | 1 | r |

| 1        | 1 | 0 | 0 | S |

| 1        | 1 | 0 | 1 | t |

| 1        | 1 | 1 | 0 | u |

| 1        | 1 | 1 | 1 | v |

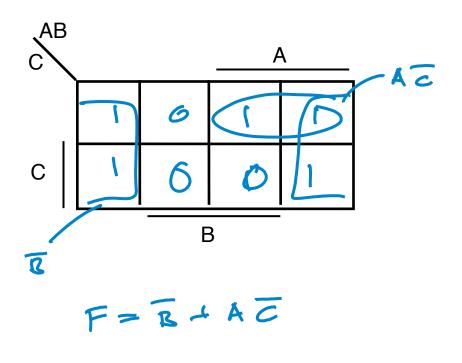

\* Convert the Truth Table to a K-Map, then solve.

| A | В | C | F | _ |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 |   |

| 0 | 0 | 1 | 1 |   |

| 0 | 1 | 0 | 0 |   |

| 0 | 1 | 1 | 0 |   |

| 1 | 0 | 0 | 1 |   |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 |   |

| 1 | 1 | 1 | 0 |   |

|   |   |   |   |   |

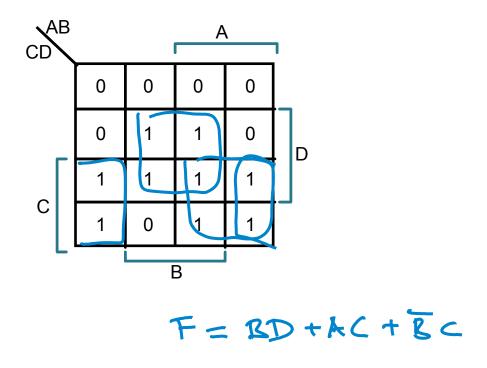

\* Solve this K-Map.

\* Solve the following K-Map.

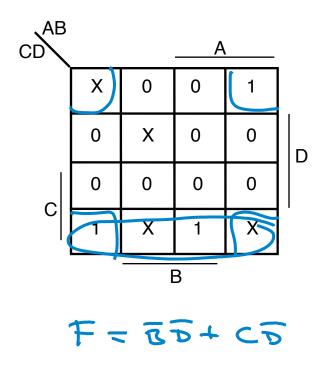

\* Solve the following K-Map.

\* Extend this Verilog code to also show the letter "A" on input pattern 1010 (ten) and "F" on pattern 1111 (fifteen).

```

[3:0] bcd;

input

output reg [6:0] leds;

L0

4'61010: (els=761110111 always @ (*)

case (bcd)

4 / 1111: leds = 7 / 5 1110001

// BCD[]

LEDS[]

// 3210

6543210

4'b0000: leds = 7'b0111111;

4'b0001: leds = 7'b0000110;

L6

4'b0010: leds = 7'b1011011;

4'b0011: leds = 7'b1001111;

4'b0100: leds = 7'b1100110;

4'b0101: leds = 7'b1101101;

4'b0110: leds = 7'b1111101;

4'b0111: leds = 7'b0000111;

L3

4'b1000: leds = 7'b11111111;

4'b1001: leds = 7'b1101111;

default: leds = 7'bX;

endcase

```

endmodule

\* Amy, Bill, Carol, and Dennis each decide independently whether they want to play Chess or Checkers, each a 2-player game. Develop a circuit that can tell if the 4 people can be organized into two simultaneous games, respecting each person's choice.

|      | r r r r     |               |  |

|------|-------------|---------------|--|

| ABOO | O 0 - 0 - 1 | GENEON, O O I |  |

| 01   | 06          | 0             |  |

| (0)  | 00101       | 00            |  |

| ll . | 00000       | 0             |  |

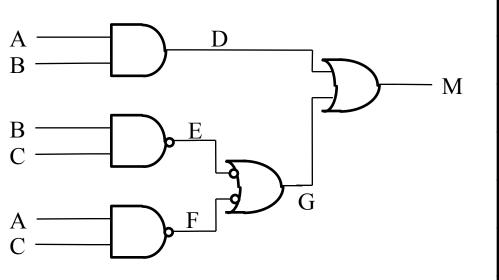

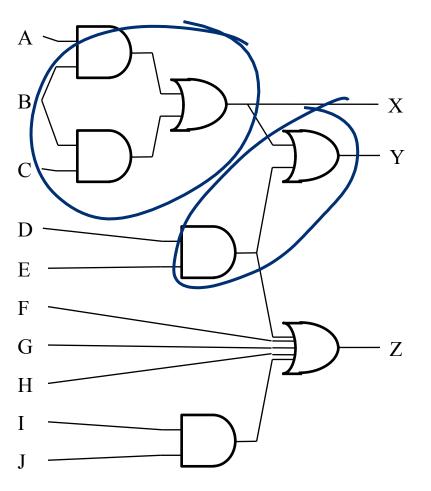

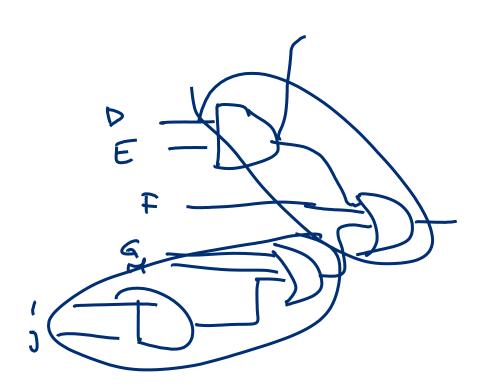

\* For the buggy majority circuit below, the expected and the measured results are shown in the table. What gate is broken in this circuit?

| Signal | Expected | Measured |

|--------|----------|----------|

| A      | 0        | 0        |

| В      | 1        | 1        |

| С      | 1        | 1        |

| D      | 0        | 0        |

| Е      | 0        | 1        |

| F      | 1        | 1        |

| G      | 1        | 0        |

| M      | 1        | 0        |

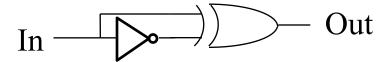

Can this circuit ever output a FALSE?

\* The following two flip-flops are subtly different, but both useful. The difference in code is shown in bold. What is the difference in their behavior?

```

module D_FF1 (q, d, reset, clk);

output q;

input d, reset, clk;

reg q;

always @(posedge clk)

if (reset)

q <= 0;

else

q <= d;

endmodule</pre>

```

```

module D_FF2 (q, d, reset, clk);

output q;

input d, reset, clk;

reg q;

always @(posedge clk or posedge reset)

if (reset)

q <= 0;

else

q <= d;

endmodule</pre>

```

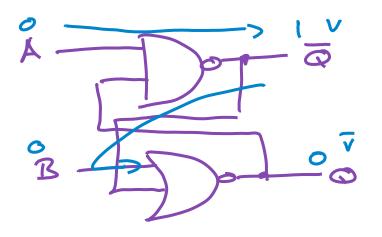

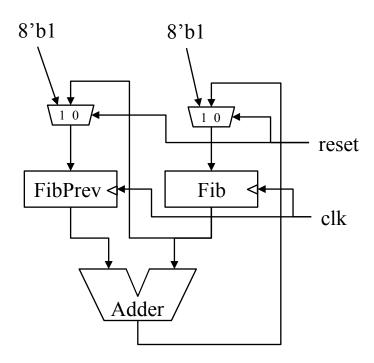

# REVIEW PROBLEM 23R

FIGURE OUT WHAT THE FOLLOWING CIRCUIT DOES.

ARE A AND B SET OR RESET SIGNALS? ACTIVE LOW OR KIGH?

A IS AN ACTIVE LOW RESET

B IS AN ACTIVE HIGH RESET

| X -y | MAND | MGR |

|------|------|-----|

| 06   | 1    | (   |

| 01   | ١    | G   |

| lG   | 1    | 6   |

| 1.1  | ð    | 6   |

|      |      | 1   |

❖ In class we said we shouldn't put a logic gate on the clock input of a flipflop because of glitches. Does this fix the problem?

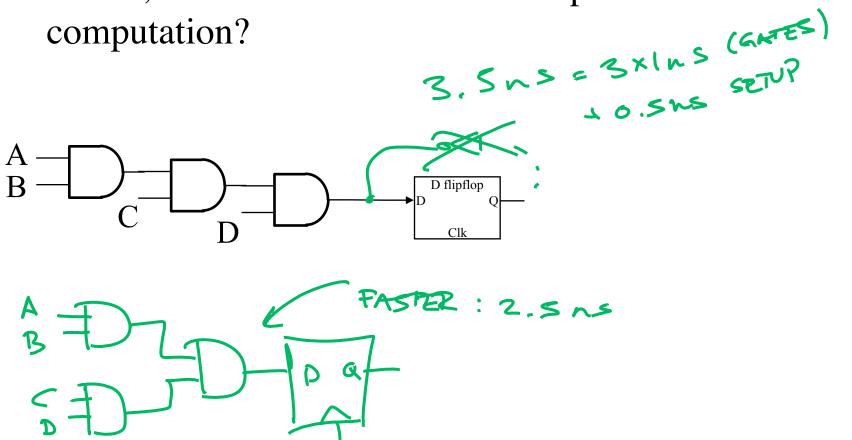

\* If gate delays are 1.0ns each,  $T_{setup}$  is 0.5, and  $T_{hold}$  is 1.5, what is the best clock period for this computation?

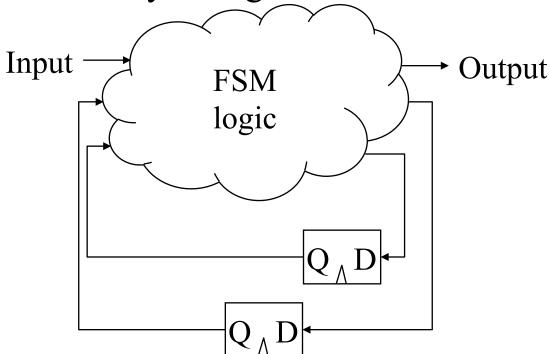

- ❖ Given the light display shown, build the FSM for a "move left" arrow traffic sign. It should animate an arrow moving left

- Hint: Can any of the bulbs be connected to the same signal?

What is the series of inputs that will produce the most TRUEs on the output

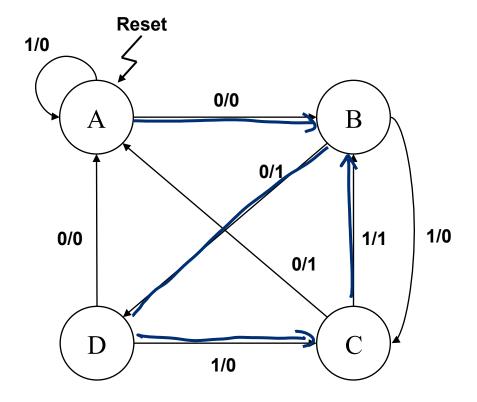

An ambulance company wants a flashing yellow light that, when a button is held, will instead hold a solid red. Design this machine.

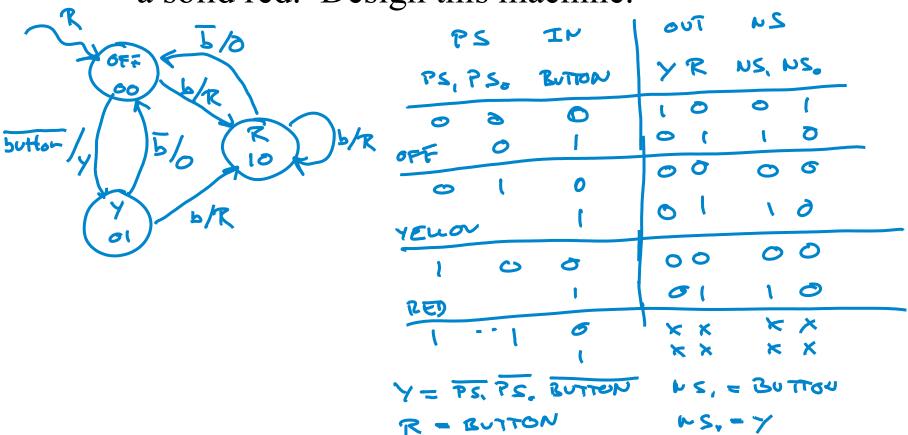

## Draw the circuit diagram for this code

```

module foo (clk, reset, in, out);

input clk, reset, in;

output reg out;

parameter A = 1'b0, B = 1'b1;

reg ps, ns;

always @(*) begin

case (ps)

A: ns = B;

B: if (in) ns = B;

default: ns = 1'bX;

endcase

out = ps;

end

always @(posedge clk)

if (reset) ps <= 1'b0;

else ps <= ns;

endmodule

```

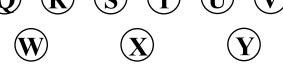

\* What does this FSM do?

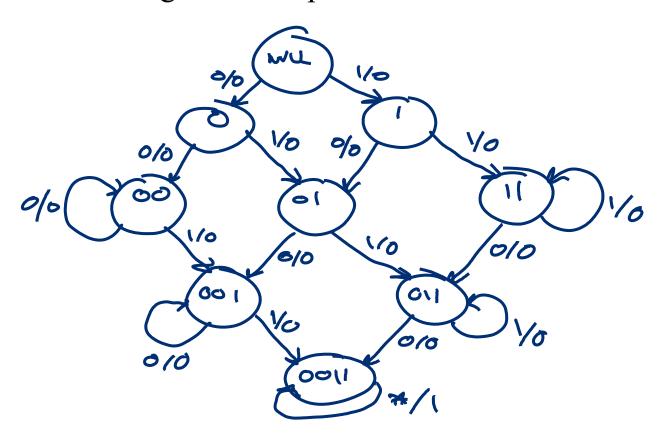

\* Draw the state diagram of a machine that continuously outputs a true once at least two 0's and at least two 1's (in any order, not necessarily consecutively) have been seen, not including current input.

\* Highway onramps have lights to meter cars entering the highway. Design the FSM for this, assuming we have a separate timer.

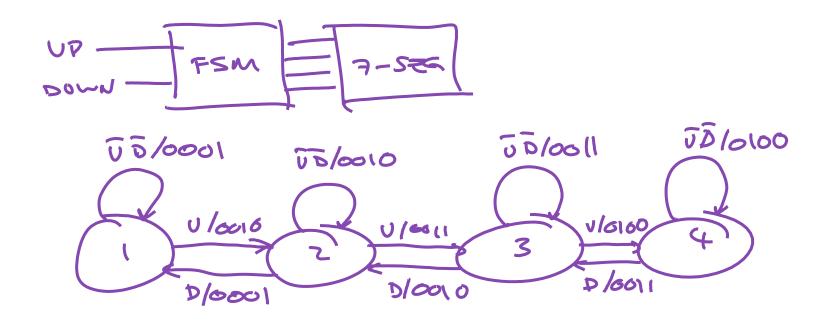

❖ Design a circuit to control the 7-segment display as an elevator floor indicator for a 4-story building.

Which of the following numbers represents the largest value?

\*

$$(10011)_2$$

= 1 + 2 + 16 = ( $\int_{16}$  (octal)

\*  $(23)_8$  = 2×8+3=15...

\*  $(13)_{16}$  = 1 × 16 + 3 = ( $\int_{16}$

- Convert the following value to binary

- **\*** (1000)<sub>10</sub>

- Perform the following conversions

- $(110101001011101010)_2$  to hexadecimal

$4(4AF3)_{16}$  to binary

Perform the following binary computations.

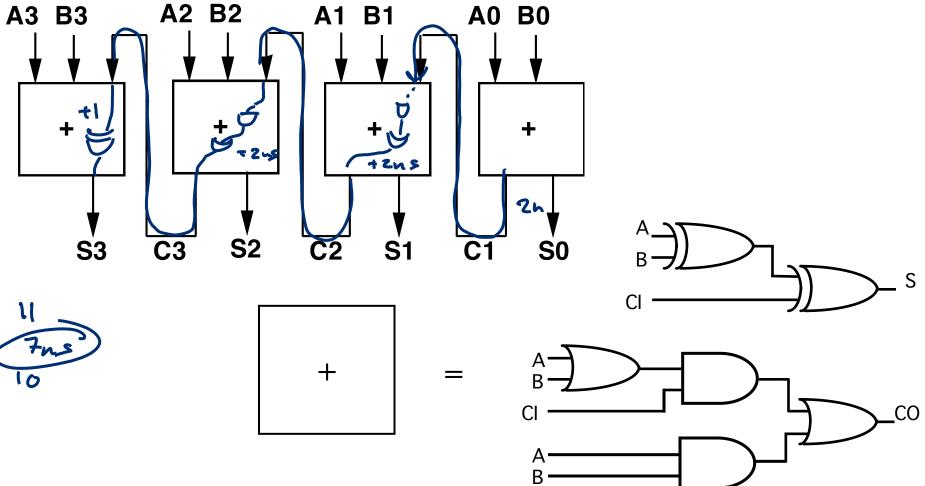

❖ If all gates have a delay of 1ns, how long does a 4bit adder take to compute?

\* Create a **truth table** for a circuit which tells if a 3-bit number is evenly divisible by 3 (num/3 leaves no remainder). Have a separate output for the unsigned, 2's comp, and sign-magnitude versions.

| B2 B1 B0 | Uns | S-M | 2's |

|----------|-----|-----|-----|

|          |     |     |     |

|          |     |     |     |

|          |     |     |     |

|          |     |     |     |

|          |     |     |     |

|          |     |     |     |

- Perform the following computation in 2's Complement & Sign/Magnitude

- \* Hint: convert subtraction to addition of the negation

2's Complement:

Sign/Magnitude:

- Convert the following numbers to decimal

- ❖ (1001) in 2's Complement:

- \* (1001) in Sign/Magnitude:

- ❖ (0101) in 2's Complement:

- \* (0101) in Sign/Magnitude:

- ❖ For the 6-bit 2's Complement number (111010)

- \* How would it be represented in 10-bit 2's Complement?

\* What's the smallest number of bits required to represent that number in 2's Complement?

\* An office building has an automatic lighting system based on motion sensors. An individual office light should be on if motion has been detected in the office within the last 5 minutes. Hallway lights should be on if any office lights on that hallway have been on, or any motion in the hallway detected, during the last 10 minutes. Design the system.

| Office    | Office | Office | Office | Office |  |  |

|-----------|--------|--------|--------|--------|--|--|

| A         | В      | C      | D      | E      |  |  |

| Hallway H |        |        |        |        |  |  |

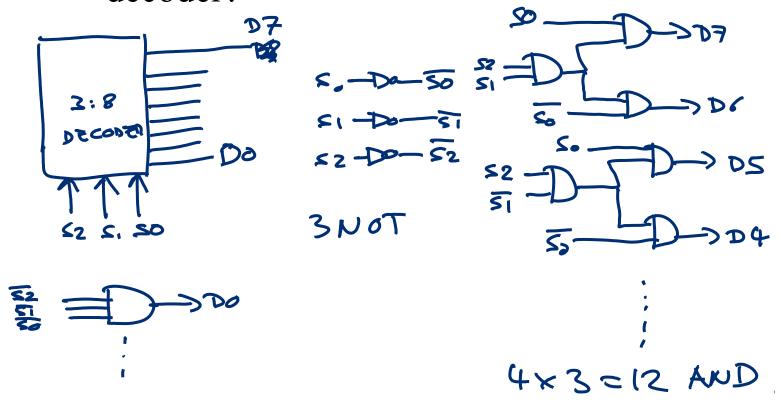

\* If we only have inverters and standard 2-input gates, how many gates are needed to build a 3:8 decoder?

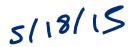

❖ Build a full adder using 3:8 Decoders and as few other gates as possible.

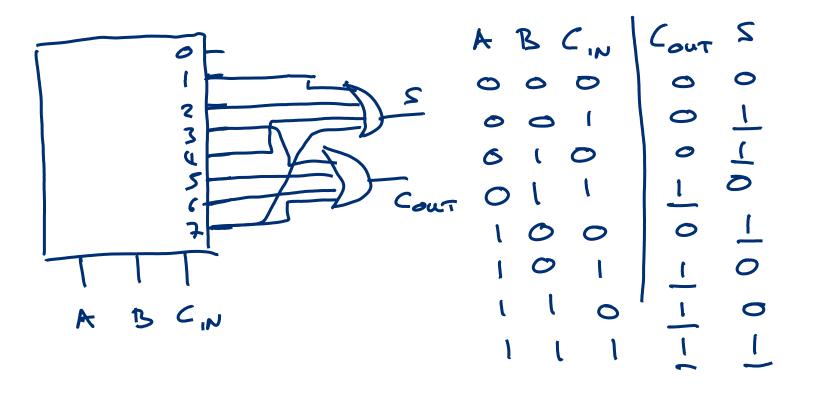

\* Instead of a priority encoder, we plan to use the basic 4:2 encoder. However, we want an output "invalid" which is true when the encoder's assumption that only one input is true is not met. Design the circuit for this output.

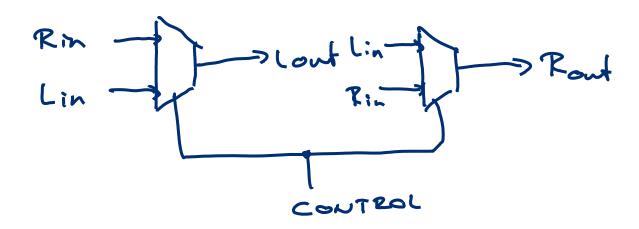

\* For a stereo, design a crossover box to deal with swapped speaker cables using **only muxes**.

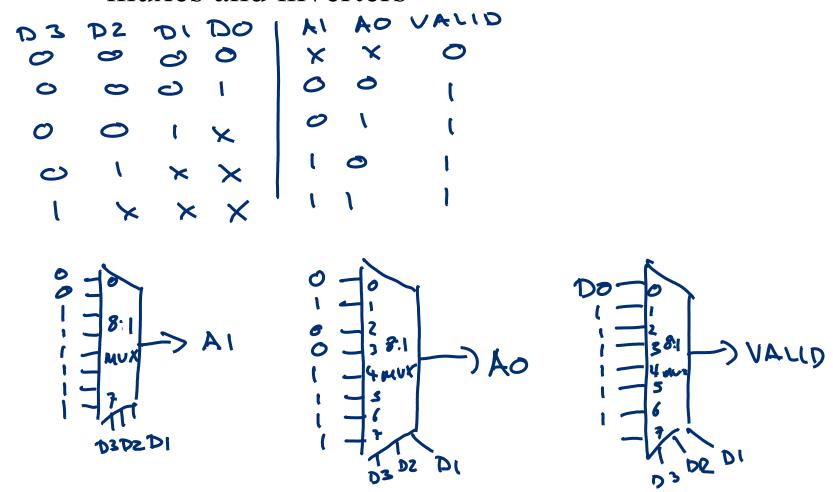

❖ Implement a 4:2 priority encoder using only 8:1 muxes and inverters

\* Implement the controlled register from lecture in Verilog.

\*\*Module reg4 (outs reset aloads de clk):

```

module reg4(out, reset, load, d, clk);

output reg [3:0] out;

elseil (load)

1 out tout; I BELAUSE

end

Permes FF

endmodule

```

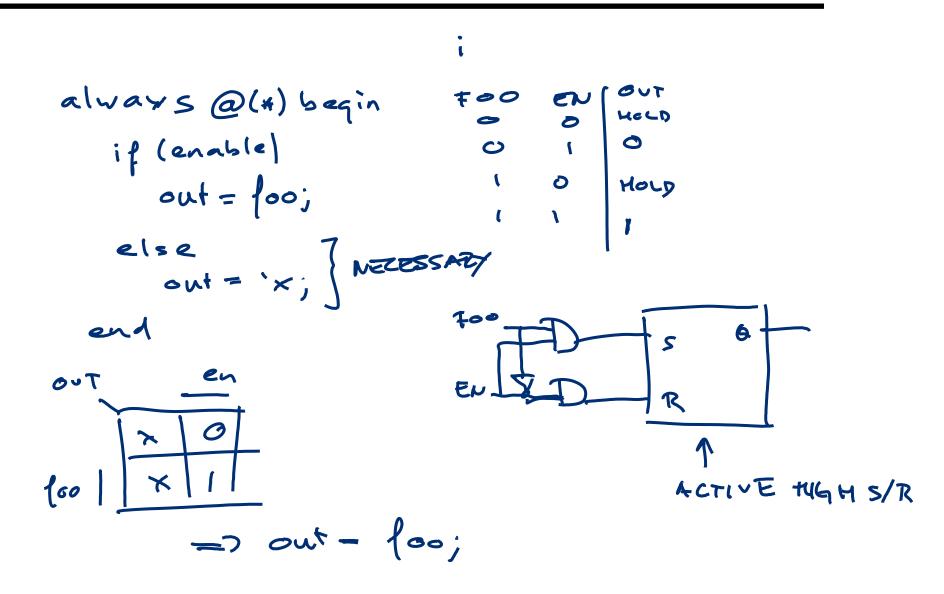

# PROBLEM 4JL: INFERRED LATCHES

❖ Given what we know about about shift registers, what are the options for sending 32-bit values?

Wires Cycles Method

❖ I have already built an FSM to run at 5MHz, but I now need to use a 50MHz clock. How can I get it to still only change states 5M times a second?

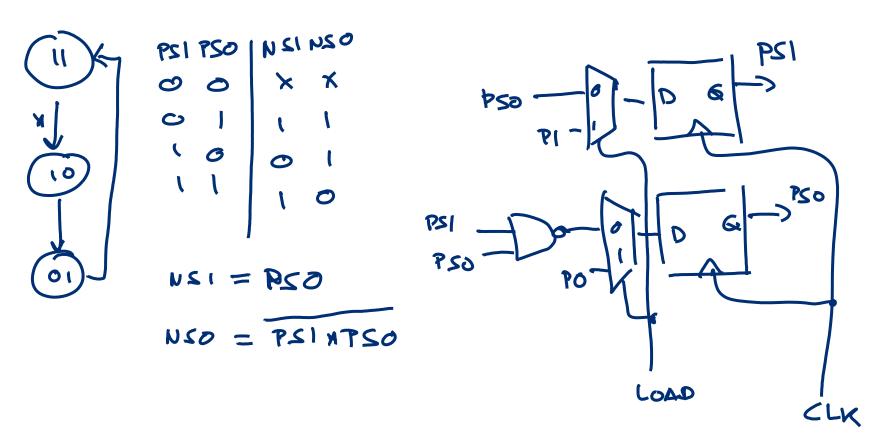

❖ Design a down counter that goes from 3 to 1 (then back to 3), with a parallel load.

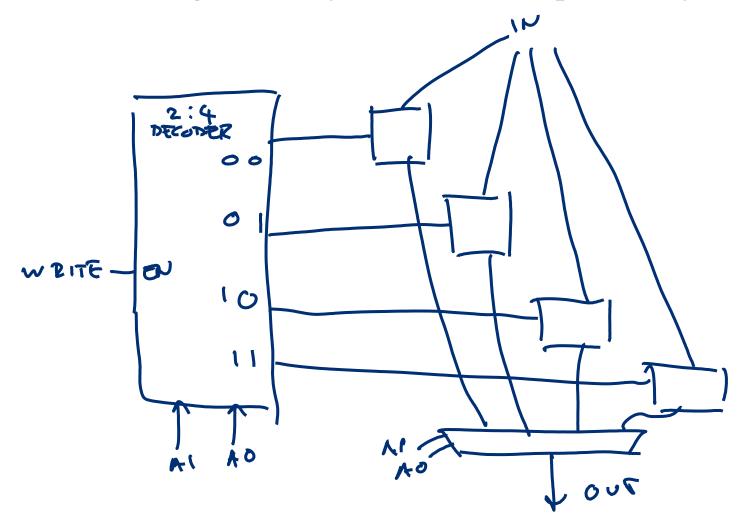

❖ Build a 4x1 RAM. Use premade RAM cells, along with any standard components you need.

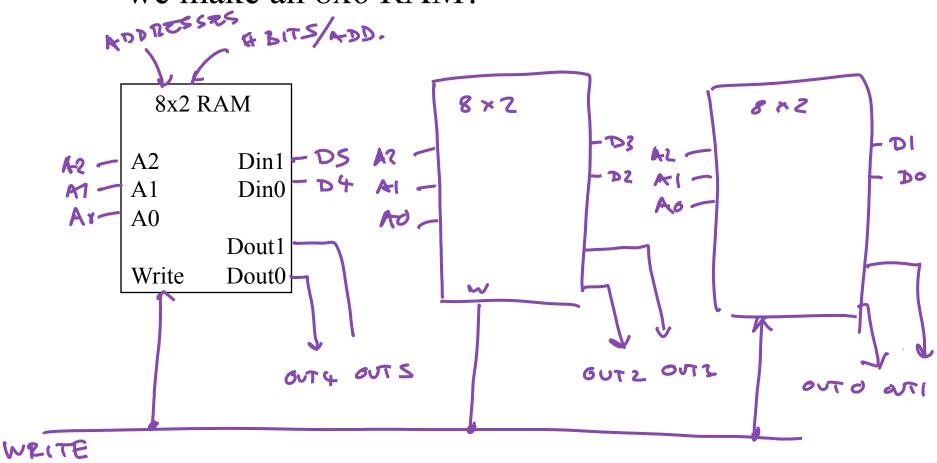

❖ If we only had 8x2 memories available, how could we make an 8x6 RAM?

\* Implement this circuit with 4-LUTs

\* What components are on your DE1-SoC board, and how are they connected?

\* Is the following good Verilog? If not, fix it. If so, draw the circuit it represents.

```

reg a, b, c;

always @(*) begin

b = 0;

c = 0;

if (a)

b = c;

else

c = b | d;

end

```

\* Write Verilog that would create this circuit.

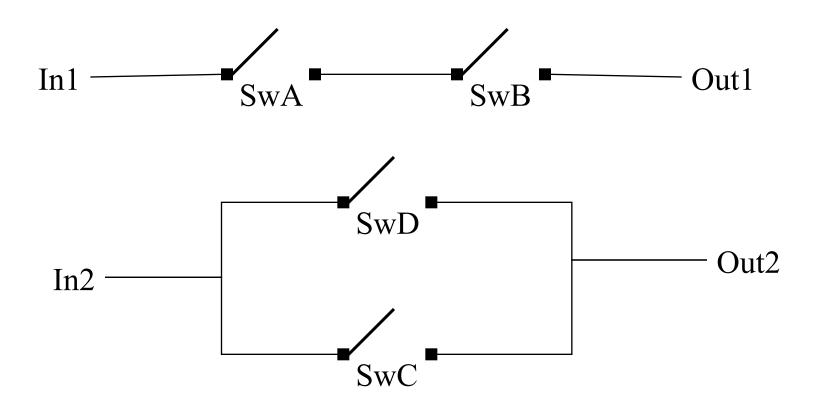

\* When will current flow from the input to the output for each of these?

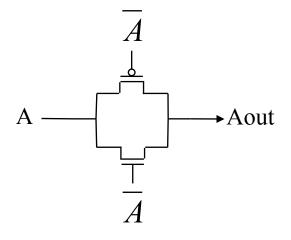

\* What do these circuits do?

❖ Build an XOR gate from transistors. Assume you have two inputs, A and B, as well as their inverses (Ā and B).